Slide 39 of 43

Notes:

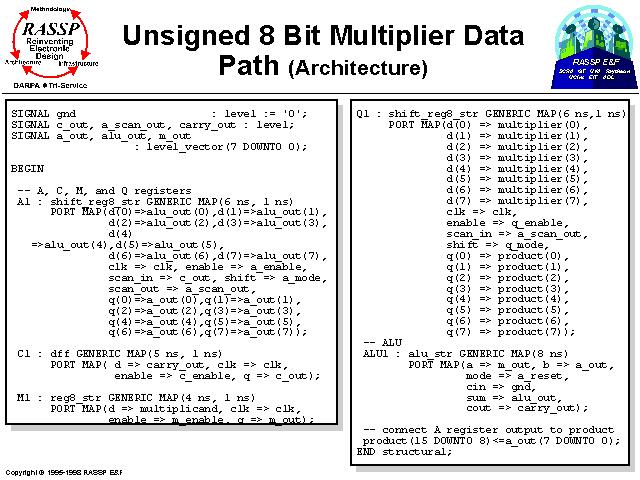

This is the component instantiations for the datapath. The mapping of individual bits of the D and Q input and output of the shift registers is necessary to reverse the inputs and outputs. Recall that the shift register was a “shift up” type where the scan_in input goes to D(0) and D(0) to D(6) go to D(1) to D(7) when in shift mode. What is needed for the multiplier is a “shift down” type register where scan_in goes to D(7), etc.

It should have been possible (we believe) to use the syntax

in the shift_reg8_str PORT MAP to accomplish the same thing, but the QuickVHDL compiler gave a “warning” and the simulator crashed, so we don’t know if it really should work.