Slide 8 of 65

Notes:

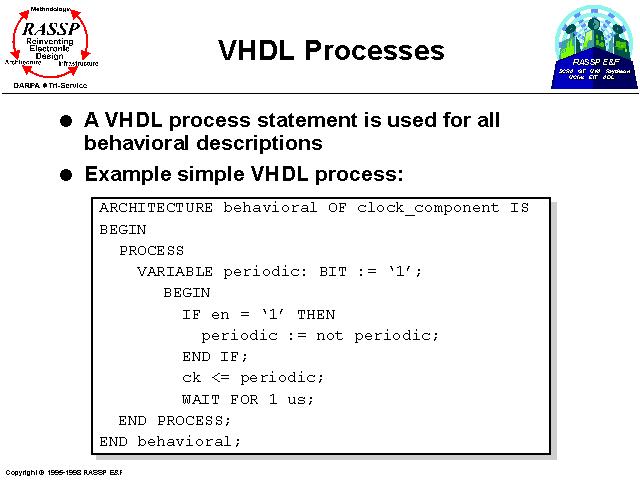

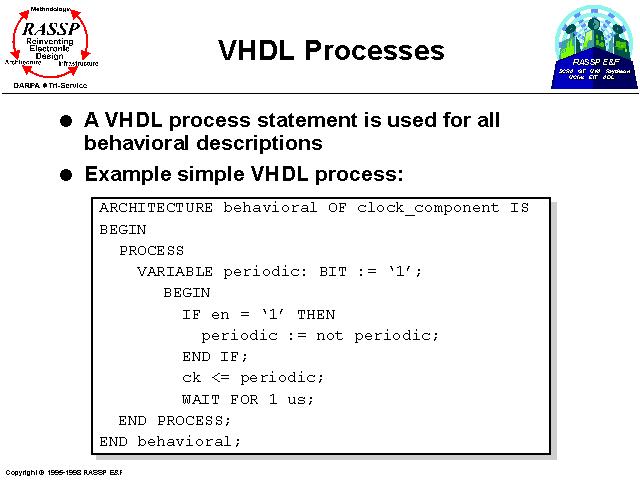

We now turn our attention to a the VHDL process statement. The process is the key structure in behavioral VHDL modeling. A process is the only means by which the executable functionality of a component is defined. In fact, for a model to be capable of being simulated, all components in the model must be defined using one or more processes.

Statements within a process are executed sequentially (although care needs to be used in signal assignment statements since they do not take effect immediately; this was covered in the VHDL Basics module when the VHDL timing model was discussed). Variables are used as internal place holders which take on their assigned values immediately.

All processes in a VHDL description are executed concurrently. That is, although statements within a process are evaluated and executed sequentially, all processes within the model begin executing concurrently.

In the example process given here, the variable periodic is declared and assigned the initial condition '1'. As long as en is '1', periodic changes value leading to a potentially new value (called a transaction) to be scheduled for ck by the simulator. The process then suspends for one microsecond of simulation time. The signal ck actually assumes its new value one delta cycle after the process suspends . After the one microsecond suspension, the process once again executes beginning with the IF statement. Note that only variables can be declared in a process, and signals (declared outside of a process) are used primarily for control (e.g., en in this case), inputs into a process, or outputs from a process (e.g., ck in this case).