Slide 44 of 65

Notes:

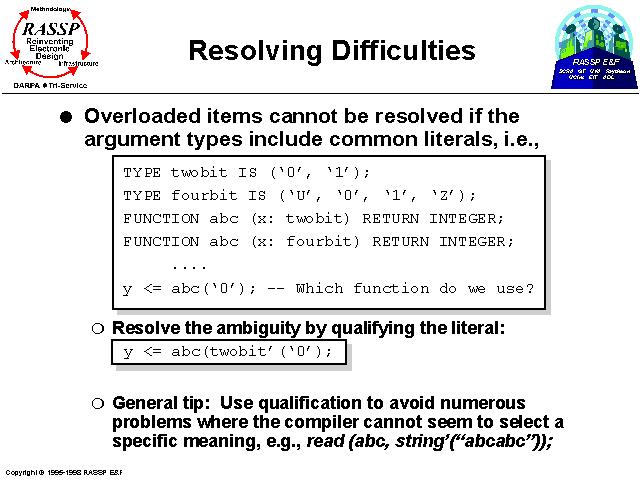

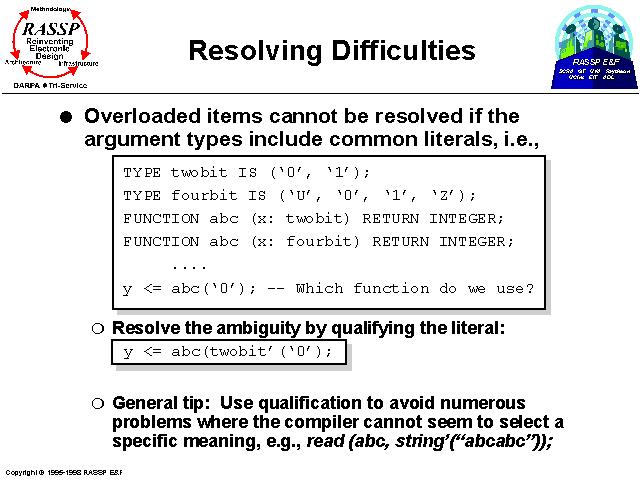

Because literals in VHDL are semantically ambiguous (e.g., “abc” can be a string or a vector of enumerated values ‘a’, ‘b’, ‘c’), it is often impossible for the VHDL analyzer to determine the exact type of a literal, and thus resolve the overloaded function, if it is dependent on the literal.

For instance, note that in the upper example, '0' appears in the definition for both enumerated types, twobit and fourbit. Therefore, calling abc with '0' as its parameter does not allow for a distinction between the two versions of the abc function.

It is a good idea to use qualification when passing literals as subprogram parameters both to ensure that inadvertent ambiguities are avoided and to improve the readability of the VHDL code.