Slide 26 of 65

Notes:

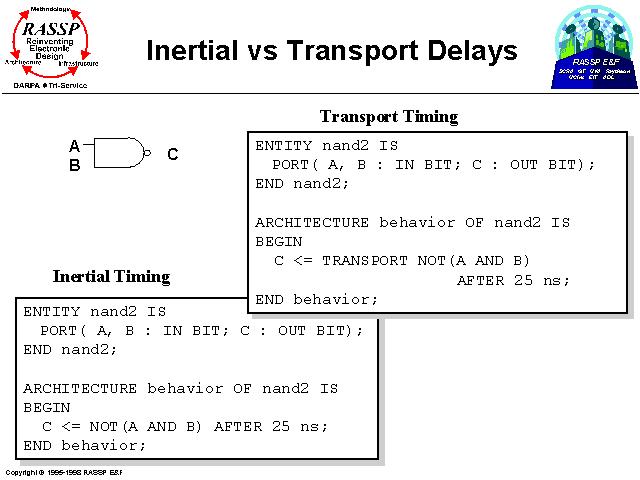

Note that in the example on the left, a 20ns pulse on A would initially result in an assignment to C to be scheduled 25ns in the future as a result of the first transition on A. However, the second transition on A (defining the 20ns pulse) would schedule a second transition on C such that C would then itself show a 20 ns pulse. This leads to both the assignments to A being suppressed so that the inertial timing requirements are satisfied.

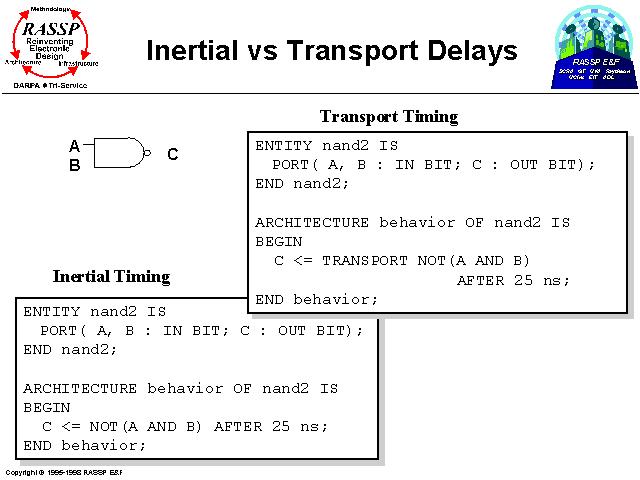

Since the example on the right explicitly calls for a transport delay (inertial delay is the default if neither form is specified), a 20ns pulse on C is allowed even when the NAND gate has a 25ns propagation delay.