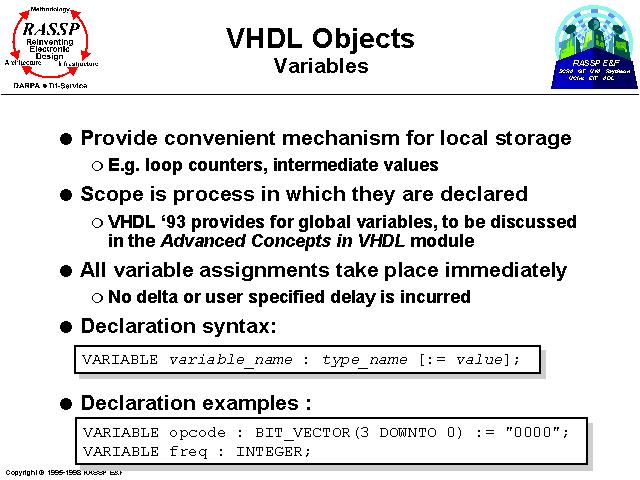

Slide 59 of 93

Notes:

This discussion about VHDL variables does not include global (aka shared) variables which were introduced in the 1076-1993 standard. The discussion of shared variables is deferred to the 'Advanced Concepts in VHDL Module'.

An important feature of the behavior of VHDL variables is that an assignment to a VHDL variable results in the variable assuming its new value immediately (i.e. no simulation time or delta cycles must transpire as is the case for VHDL signals). This feature allows the sequential execution of statements within VHDL processes where variables are used as placeholders for temporary data, loop counters, etc.

Examples of variable declarations and assignments are shown above. Note that when a variable is declared, it may optionally be given an initial value as well.