Slide 31 of 93

Notes:

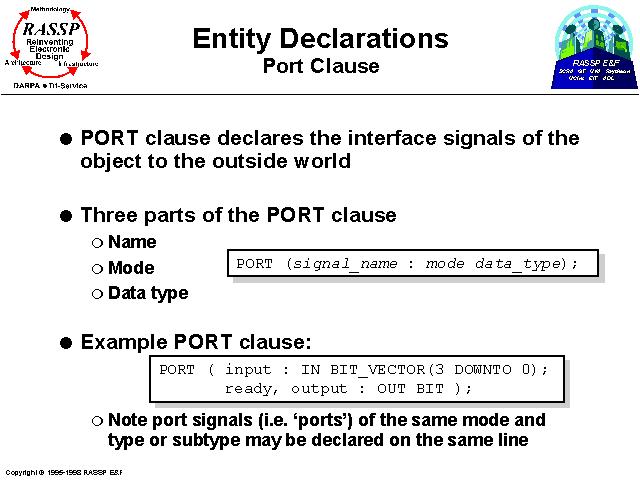

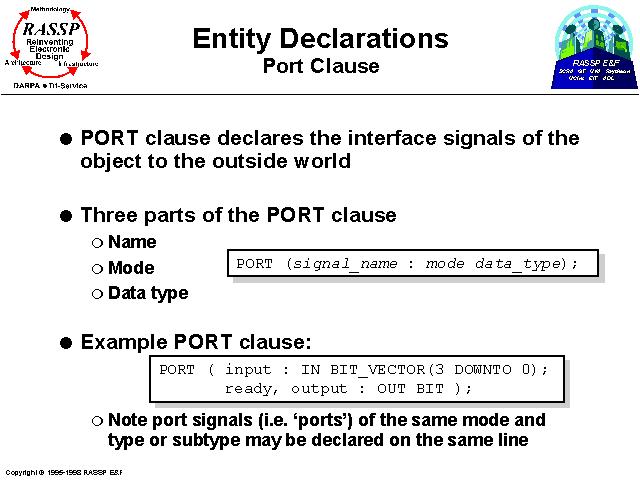

The PORT declaration describes the interface of the component. There are three essential elements to the port declaration: the name, mode, and type of the signals in the interface. An optional fourth element (not shown above) in a port declaration is the signal’s initial value which will be assigned to the signal as a default if there are no active drivers on the signal at the start of a simulation.

Note that signals declared in an entity's port declaration may sometimes be referred to as ports.

In the example port declaration above, input is an input and can only be read by the device. The ports ready and output are outputs so that the signals are "driven" by this component. Note that according to the 1076-1987 VHDL Standard, a component could not read its own OUT ports; this awkwardness was corrected the 1076-1993 VHDL Standard.

Finally, the port must indicate the type or subtype for port signals. Any VHDL-defined standard or user-defined type or subtype may be used in a port declaration. Note that a range specification may be declared if an unconstrained type is used in the type declaration.